# Phase-Shift Control for High-Voltage DC-Based System with Modular Multi-Level DC/DC Converter

<sup>1</sup>H.Vijayalaxmi, <sup>2</sup>S.Papa Rao

<sup>1</sup>Pursuing M.Tech, PE Branch, Dept of EEE, Brilliant Institute of Engineering and Technology <sup>2</sup>Asst.Prof,EEE, Dept, Brilliant Institute Of Engineering and Technology

Abstract: Dc-based distributions and dc-based micro grids are recognized as the promising solutions for future smart-grid systems due to their clear advantages of flexibility for photovoltaic and fuel cells interface, without frequency stability, high conversion efficiency, and easy system control. The Modular Multilevel Converter (MMC) represents an emerging topology with a scalable technology making high voltage and power capability possible. The MMC is built up by identical, but individually controllable sub modules. A control scheme with a new sub module capacitor voltage balancing method is also proposed in this paper. Modular multilevel converters, based on cascading of half bridge converter cells, can combine low switching frequency with low harmonic interference. They can be designed for high operating voltages without direct series connection of semiconductor element. The high switch voltage stress in the primary side is effectively reduced by the full bridge modules in series. In this paper by investigating by investigating the topology derivation principle of the phase-shift-controlled three-level dc/dc converters, the modular multilevel dc/dc converters, by integrating the full bridge converters and three-level flying capacitor circuit, the proposed concept is implemented to control of DC motor using modular dc-dc converter with MATLAB/SIMULINK software.

**Keywords:** Input Voltage Auto Balance, Modular Multilevel DC/DC Converter, Phase-Shift Control Scheme, Zero-Voltage Switching (ZVS).DC Motor

# I. INTRODUCTION

The modular multilevel converter (MMC)-based high voltage directs current (HVDC) system is a new type of voltage source converter (VSC) for medium or high voltage direct current power transmission. Recently, it has become more competitive because it has advantages over normal VSC-HVDC system such as low total harmonic distortion, high efficiency, and high capacity [1, 2]. The operation of the MMC-HVDC system has been investigated by many authors over the world. In [3-5], the authors presented the control strategies for eliminating the circulating currents and maintaining the capacitor voltage balancing of the MMC. The dynamic performances of the MMC-HVDC system have been analyzed in [6]. Similar to other HVDC systems, the stable and reliable operation of the system must be researched carefully, especially when the system operates under fault conditions. In [6-8], the authors showed out the control methods of the MMC-HVDC system under the unbalanced voltage conditions. Almost all of them only focus on the use of proportional-integral (PI) current controllers in the synchronous rotating reference frame (dq-frame) for enforcing steady-state error to zero.

However, the use of these PI current controllers will be difficult under the unbalanced voltage conditions because of the complex control of the positive and negative sequence components of the currents [6-8].Recently, the simple proportionalresonan (PR) current controllers in the stationary reference frame ( $\alpha\beta$ -frame) have been developed to overcome this problem [10]. The most important performance of the PR current controllers is that the currents are controlled directly in the  $\alpha\beta$ -frame. Therefore, the complicated analysis of the positive and negative sequence components of the currents is ignored. In this paper, the flying capacitor and fullbridge converters are combined and integrated to derive the advanced modular multilevel dc/dc converters for the high step-down and high power dcbased conversion applications. Due to the charging and discharging balance of the built-in flying capacitor, the input voltage auto balance ability is naturally realized, which halves the switch voltage stress and overcomes the input voltage imbalance. Furthermore, the phase-shift control strategy can be adopted to achieve the soft-switching operation and reduce the switching losses. The concept of modular

multilevel dc/dc converters may provide a clear picture on high-voltage dc/dc topologies for the dc-based distribution and micro grid systems.

# II. DERIVATION LAW OF MODULAR MULTILEVEL CONVERTERS

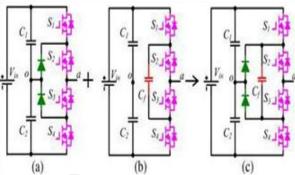

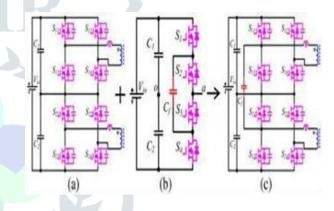

The derivation process of the proposed modular multilevel dc/dc converters is discussed in this section. It is well known that the neutral-point-clamped (NPC) converters and flying capacitor-based converters are the major multilevel topologies for the high-voltage and high-power applications. For the conventional NPC converters with pulse width modulation control, the abnormal operation condition, such as the mismatch in the gate signals, may cause the voltage imbalance of the input capacitors. Therefore, the converter reliability is impacted. Furthermore, the phase-shift control scheme is not suitable for the conventional NPC converters, which leads to large switching losses. Fortunately, by inserting a small flying capacitor parallel connected with the clamping diodes, the input capacitor voltages are automatically shared because the flying capacitor can be directly parallel with the series input capacitors alternatively. More importantly, the phase-shift control strategy can be easily applied to achieve zero-voltage-switching (ZVS) operation without adding any other power components. The phase-shift controlled three-level dc/dc converter is plotted in Fig. 1(c). From another point of view, the phase-shift-controlled TLC can be regarded as the combination and integration of the three-level NPC converter as given in Fig. 1(a) and the three-level flying capacitor-based circuit as shown in Fig. 1(b), where the input capacitors and active power switches are reused and shared to reduce the circuit complexity. As a result, the advantages of the NPC converter and flying capacitor-based circuit are kept whereas their inherent disadvantages are effectively avoided. Many further improvements are made for the combined phase shift-controlled TLC by adding some active or passive components to extend the softswitching operation range.Based on the previously summarized combined multilevel derivation principle, it is innovative and attractive to consider the possibility of combination of the other fundamental multilevel topologies. For example, the cascaded fullbridge converter, or the ISOP full-bridge converter, and the three-level flying capacitor-based converter are combined and integrated to derive the advanced modular multilevel dc/dc converters, which is detailed illustrated in Fig. 2. The time sequence of the leading leg in the phase-shift-controlled full-bridge converters is kept constant and only the phase of the

Fig.1. Derivation of novel TLC: (a) NPC TLC, (b) flying capacitor-based TLC, and (c) phase-shiftcontrolled combined TLC.

Fig.2. Derivation of the proposed modular multilevel dc/dc converter: (a) cascaded full-bridge converter, (b) flying capacitor-based TLC, and (c) proposed modular multilevel dc/dc topology.

lagging leg is shifted to regulate the output voltage. This indicates that the leading legs of the cascaded fullbridge converter can be assembled with the three-level flying capacitor-based converter to achieve the input voltage auto balance. And the lagging legs of the cascaded full bridge converter are still kept unchanged to provide adequate control freedom to achieve fast and accurate output voltage regulation. Consequently, for the proposed modular multilevel dc/dc converters, the big concern of the input-voltage imbalance existed in the ISOP converters is completely overcome due to the built-in flying capacitor. More importantly, the derived modular multilevel dc/dc concept can be easily put forward to N-stage converters by stacking the full-bridge power modules in series in the primary side to satisfy the growing bus voltage in the dcbased distribution and micro grid systems. In view of the phase-shift-controlled topologies, the aforementioned optimized strategies for the phase-shifted-controlled TLCs

can be directly transferred to the derived modular multilevel dc/dc converters to generate a family of high performance topologies for the high-voltage and high-power applications. It can be concluded that this modular multilevel converter concept is one of the general solutions for the high-voltage and high-power dc/dc topology origination

# III. OPERATIONPRINCIPLE AND INPUTVOLTAGE AUTOBALANCE MECHANISM

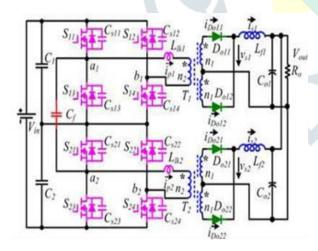

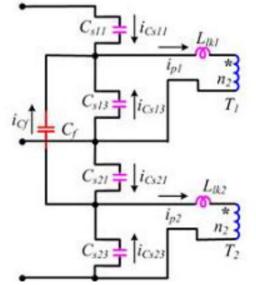

For the secondary side of the derived modular multilevel dc/dc converters, the current-type full-wave rectifier, full-bridge rectifier, current doubler rectifier, and other advanced current-type rectifiers can be employed. In this section, the widely adopted currenttype full-wave rectifier is applied as an example to explore the circuit performance of the proposed modular multilevel configuration, which is illustrated in Fig. 3. In the primary side, the capacitors Cland C2are used to split the high input voltage, S11–S14are the power switches of the top full-bridge module, S21–S24form the bottom full-bridge module,Cs11-Cs24are the parasiticcapacitors of the power switches, and Llk1and Llk2 are the leakage inductors of the transformersT1andT2, respectively.

In the secondary side, Do11,Do12,Lf1, and Co1 are for the top full-bridge module and Do21,Do22,Lf2, and Co2 are for the

Fig.3. Proposed modular multilevel dc/dc converter with input voltage auto balance ability. bottom full-bridge module.  $i_{p1}$ ,  $i_{p2}$ ,  $i_{D011}$ ,  $i_{D012}$ ,  $i_{D022}$  are the primary and secondary currents through the windings of

the transformers with the defined direction in Fig. 3. And  $i_{s1}$  and  $i_{s2}$  are the filter inductors currents

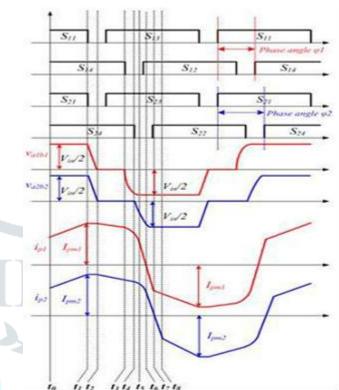

### Fig.4. Key waveforms of the proposed converter. A. Operation Analysis

The phase-shift control scheme is employed in the proposed converter to realize the ZVS performance of all the power switches, where S<sub>11</sub>,S<sub>13</sub>,S<sub>21</sub>, and S<sub>23</sub> are the leading-leg switches and S<sub>12</sub>,S<sub>14</sub>,S<sub>22</sub>, and S<sub>24</sub> are the lagging-leg switches. The key waveforms of the proposed converter are shown in Fig. 4. For the top full-bridge module,  $S_{11}$  and  $S_{13}$  act with 0.5 duty cycle complementarily with proper dead time td, so as for the switches  $S_{12}$  and  $S_{14}$ . The phase-shift angle between the leading and lagging switch pairs is defined as  $\phi_1$ . The gate signal pattern of the bottom full-bridge module is similar to that of the top full-bridge module with the phase-shift angle  $\phi_2$ . Meanwhile, the leading switches pair S<sub>11</sub> and S<sub>13</sub> turns ON and OFF simultaneously with the switch pair  $S_{21}$  and  $S_{23}$ , while the phase-shift angles  $\phi_1$  and  $\phi_2$  are decoupled control freedoms for the output voltage regulation. The mode 0  $<\phi_1-\phi_2<t_d$  is taken into consideration when analyzing the operation of the converter, and the equivalent operation circuits are depicted in Fig. 5. In order to simplify the analysis, the following assumptions are made: 1) all the power switches and diodes are ideal; 2) the parasitic capacitors  $C_{s11}$ - $C_{s24}$  of the switches have the same value as Cs; 3) the voltage ripples on the divided input capacitors  $C_1, C_2$  and flying capacitors  $C_f$  are small due to their large capacitance; 4) the turns ratio of both transformers is  $N = n_2:n_1$ ; and 5) the input voltage is balanced and the auto balance mechanism will be depicted later. There are 15 operation stages in one switching period. Due to the symmetrical circuit structure and operation, only the first eight stages are analyzed as follows.

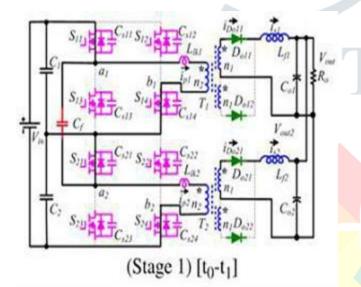

**Stage1** [ $t_0, t_1$ ]: Before  $t_1$ , the switches  $S_{11}, S_{14}, S_{21}$ , and  $S_{24}$  are in the turn-on state to deliver the power to the secondary side.

The output diodes  $D_{o11}$  and  $D_{o21}$  are conducted and the output diodes  $D_{o12}$  and  $D_{o22}$  are reverse biased. The flying capacitor  $C_f$  is in parallel with the input divided capacitor  $C_1$  to make  $V_{Cf}$  equal to  $V_{C1}$ .

$$i_{p1}(t) = i_{p1}(t_0) + \frac{V_{\rm in}/2 - NV_{\rm out}}{L_{lk1} + N^2 L_{f1}}(t - t_0)$$

<sup>(1)</sup>

$$i_{p2}(t) = i_{p2}(t_0) + \frac{V_{\rm in}/2 - NV_{\rm out}}{L_{lk2} + N^2 L_{f2}}(t - t_0)$$

<sup>(2)</sup>

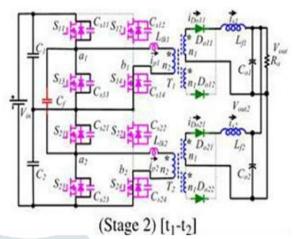

Fig.5.Stage 2 [t1,t2]:At t1, the turn-off signals of the switches S11and S 21are given. ZVS turn off for these two switches are achieved due tothe capacitors Cs11 andCs21. Cs11 andCs21 are charged andCs13 andCs23 are discharged by the primary currents.

$$i_{p1}(t) = \frac{i_{s1}(t)}{N}$$

(3)

$$i_{p2}(t) = \frac{i_{s2}(t)}{N}$$

(4)

Fig.6.

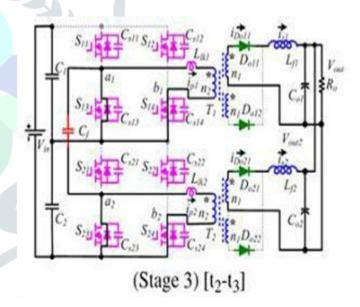

Stage3[t2,t3]:At t2, the voltages of Cs13 andCs23 reach 0 and the body diodes ofS13andS23are conducted, providing then ZVS turn-on condition forS13andS23. The flying capacitor Cf is changed to be in parallel with the input divided capacitor C2. The primary currents are derived by

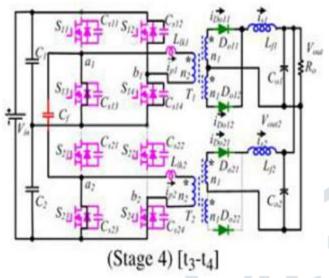

Fig.7. Stage4[t3,t4]:At t3,S14turns off with ZVS.Cs14is charged andCs12 is discharged, leading to the forward bias of Do12;i<sub>p1</sub>is regulated by  $i_{p1}(t) = i_{p1}(t_3) \cos \omega (t - t_3)$

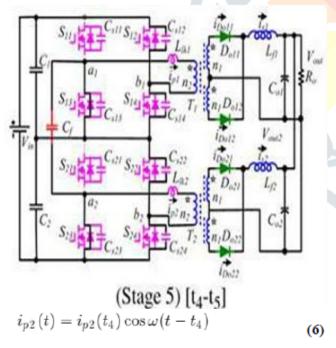

Stage5 [t4,t5]: At t4, the turn-off signal ofS24comes. ZVS turnoff performance is achieved forS24. Similar to the previous time interval, D<sub>021</sub> and D<sub>022</sub> conduct simultaneously, thus leading to the transformer T<sub>2</sub> short-circuit.ip2is regulated by

## Fig9:

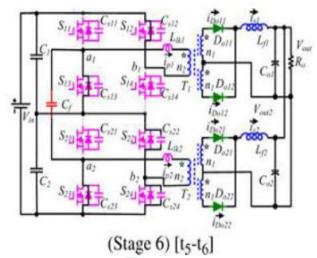

Stage 6 [t5,t6]:Att5,Cs12is discharged completely and the antiparallel diode of S12 conducts, getting ready for the ZVS Turn-on ofS12. During this time interval, ip1 declines steeply duo to half-input voltage across the leakage inductorLlk1. ip1 is given by

$$i_{p1}(t) = i_{p1}(t_5) - \frac{V_{in}/2}{L_{lk1}}(t - t_5)$$

(7)

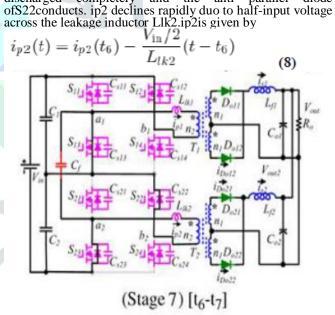

Fig 10: Stage 7 [t6,t7]:At t6,ip1 decreases to 0 and increases reversely with the same slope through S12 and S13. Cs22 is discharged completely and the anti parallel diode

Fig.11:

Stage 8 [t7,t8]:At t7,ip2 decreases to 0 and increases reversely through S22 and S23. The current through the output diodeDo11 decreases to 0 and turns off. The output diodeDo21 turns off aftert8, and then a similar operation works in the rest stages

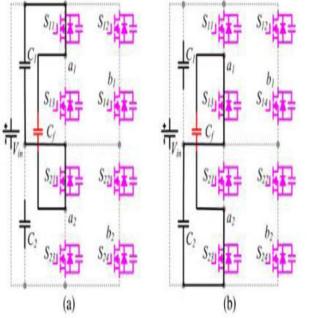

#### **B.** Input Voltage Auto balance Mechanism

The input voltage imbalance is one of the major drawbacks for most multilevel converters and ISOP converters, which is mainly caused by the asymmetry of the component parameterdifference and the mismatch of control signals. It has been carried out that the transformer turns ratio difference (N), leakage inductance distinction (Lk), and

phase-shift angle mismatch ( $\varphi$ ) are the main reasons for the input voltage imbalance in the steady state for the ISOP phase-shift-controlled converters. The effect of these factors is summarized in Table I, which shows that N1 >N2 orLik1 >Lik2 or $\phi_1$  > $\phi_2$  leads to the voltage VC1on the top input capacitorC1higher than the voltageVc2on the bottom capacitorC2and vice versa. As the parameter difference increases, the voltage gap betweenVC1andVC2increases correspondingly. The input voltage auto balance mechanism of the proposed modular multilevel dc/dc converter is displayed in Fig. 6 and detailed elaborated as follows. According to the steady operation of the proposed for leading-leg switches, converter, the the switchesS11andS21have the same time sequence and the switchesS13 andS23 are operated synchronously. WhenS11 andS21 are turned ON,S13andS23 are turned OFF accordingly, and the flying capacitor Cf is connected in parallel with the top input capacitor C1 as plotted in Fig. 12(a). This makes Vcrequal toVc1. In the same way, as given in Fig. 12(b), the flying capacitor Cris in parallel with the bottom input capacitor C2, when S13and S23are in turn-on state. This denotes that VcrandVc2 are the same. The connection of Cf with  $C_1\,\text{or}\,\,C_2$  alternates with high switching frequency, which leads to the voltages on both the input capacitors automatically shared and balanced. It is important to point out that the flying capacitor does not connect with the lagging-leg switches directly. As a result, the operation of Cfhardly affects the states of the lagging-leg switches. Then, both the two phase-shift angles  $\varphi_1$  and  $\varphi_2$  can be taken as control freedoms to regulate the output voltage.

Fig.12. Input voltage auto balance mechanism: (a)Cf in parallel withC1 and(b) Cf in parallel withC2.

#### IV. CONVERTER PERFORMANCE ANALYSIS A. Voltage Stresses of Switches

In the primary side, the voltage stress of the power switches S11–S24is half of the input voltage owing to the series structure and the auto balance mechanism. As a result, the low voltage-rated power devices are available in the high input applications to restrict the conduction losses.

#### **B. ZVS Soft-Switching Condition**

**Leading Legs:** ZVS turn-off is achieved for the leading switches due to their intrinsic capacitors. In order to realize ZVS turn-on, enough energy is needed to charge and discharge the intrinsic capacitors. During the dead time interval [t1-t2], S11 andS21 are turned OFF; Cs11 andCs21 are charged andCs13 andCs23 are discharged as shown in Fig. 13. According to the Kirchh offs law, the following equations are derived:

$$i_{Cs11} + i_{Cs13} = i_{p1} - i_{Cf} \tag{9}$$

$$i_{Cs21} + i_{Cs23} = i_{p2} + i_{Cf} \tag{10}$$

It is reasonable to assume that  $i_{p1}$  and  $i_{p2}$  are nearly constant during this period due to the short dead time. When the sum of VC<sub>s13</sub> and VC<sub>s21</sub> is not equal to Vcf, Cfmay be charged or discharged. The current iCf affects the ZVS performance of the power switches according to (11) and (12): 1) when Cfis discharged, icflows in the positive direction, and ZVS performance of S<sub>21</sub> and S<sub>23</sub> is improved but deteriorated for S<sub>11</sub> andS<sub>13</sub>; and 2) when Cfis charged, icflows reversely, which improves the ZVS performance of S<sub>11</sub> and S<sub>13</sub> but deteriorates that of S<sub>21</sub> and S<sub>23</sub>. Fortunately, Cfis much larger than Cs, making icfsmall. Besides, the output filter inductance is reflected to the primary side and is in series with the resonant inductance. The energy of both the filter inductors and the resonant inductors is sufficient to achieve ZVS for the leading switches. The output filter inductance is so large enough that the leading switches can realize ZVS turn-on even at light loads.

# Fig.13. ZVS equivalent circuit of leading switches during dead time.

**Lagging Legs:** Similar with the leading switches, the lagging switches are able to realize ZVS turn-off by utilizing their intrinsic capacitors. However, only the energies of the resonant inductors are employed to achieve ZVS turn-on for the lagging switches. In order to accomplish ZVS

$$\frac{1}{2}L_{lk}\left(\frac{I_o}{N}\right)^2 > \frac{1}{2} \cdot 2C_s \left(\frac{1}{2}V_{\rm in}\right)^2 = \frac{1}{4}C_s V_{\rm in}^2 \tag{11}$$

As the resonant inductance is quite smaller than the filter inductance, the achievement of the ZVS turn-on for the lagging switches is more difficult than the leading switches at light loads.

# C. Duty Cycle Loss

During interval [t3–t7], Va1b1 is negative, and ip1 transits from the positive direction to the negative reflected filter inductance current. The secondary diodes Do11 andDo12 conduct simultaneously, making the secondary rectified

$$D_{\text{loss1}} = \frac{2(t_7 - t_3)}{T_s} \approx \frac{8L_{lk1}I_{o1}}{NV_{\text{in}}}.$$

For the bottom full-bridge module, the duty cycle loss is similar to the top full-bridge module as given by

(12)

(13)

$$D_{\rm loss2} = \frac{2(t_8 - t_4)}{T_c} \approx \frac{8L_{lk2}I_{o2}}{NV_{\rm in}}$$

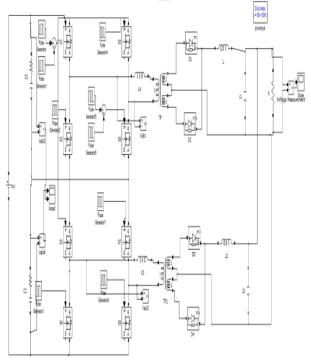

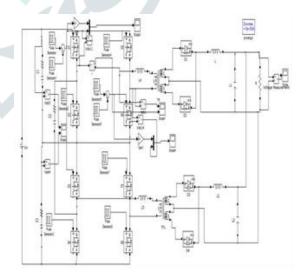

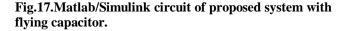

**V. SIMULATION RESULTS** Simulation results of this paper is shown in bellow Figs.14 to 20

Fig.14. Matlab/Simulink circuit of proposed system without flying capacitor.

Phase-Shift Control for High-Voltage DC-Based System with Modular Multi-Level DC/DC Converter

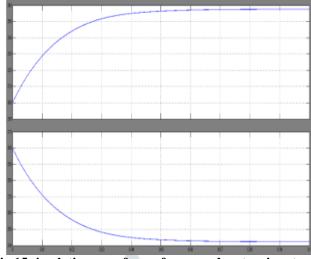

Fig.15.simulation waveform of proposed system input voltage without flying capacitor.

Fig.16. simulation waveform of proposed system output voltage without flying capacitor.

Fig.18. Simulation results of ZVS operation: (a) ZVS operation for S11 and (b) ZVS operation for S14.

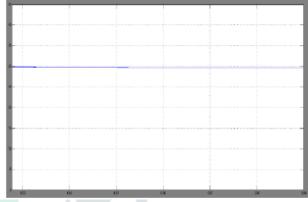

Fig.20.simulation waveform of proposed system input voltage with flying capacitor.

# VI. CONCLUSION

In this paper, proposed modular multi-level converter dc/dc converter is analyzed for the high step down and high power dc based systems, by integrating the full bridge converters and three-level flying capacitor. The presence of inherent capacitors automatically shared the input voltage and balanced without any power components and control loops. Hence it is cost effective By the input voltage balance reduces the voltage stress. By this zero voltage switching performance can be ensured hence switching losses can be decreased. The MMC can be developed for N-stages to achiechve for better performance.

# VII. REFERENCES

[1] H. Kakigano, Y. Miura, and T. Ise, —Low-voltage bipolartype DC microgrid for super high quality distribution,IIEEE

Trans. Power Electron., vol. 25, no. 12, pp. 3066–3075, Dec. 2010.

[2] S. Anand and B. G. Fernandes, —Reduced-order model and stability analysis of low-voltage DC microgrid, IIEEE Trans. Ind. Electron., vol. 60, no. 11, pp. 5040–5049, Nov. 2013.

[3] S. Anand and B. G. Fernandes, —Optimal voltage level for DC microgrids, linProc. IEEE Conf. Ind. Electron., 2010, pp. 3034–3039.

[4] D. Salomonsson, L. Soder, and A. Sannino, —An adaptive control system for a DC microgrid for data centers, I IEEE

Trans. Ind. Appl., vol. 44, no. 6, pp. 1910–1917, Nov./Dec. 2008.

[5] K. B. Park, G. W. Moon,, and M. J. Youn, —Series-input series-rectifier interleaved forward converter with a common transformer reset circuit for high-input-voltage applications, IIEEE Trans. Power Electron., vol. 26, no. 11, pp. 3242–3253, Nov. 2011.

[6] T. Qain and B. Lehman, —Coupled input-series and output-parallel dual interleaved flyback converter for high input voltage application, IEEE Trans. Power Electron., vol. 23, no. 1, pp. 88–95, Jan. 2008.

[7] C. H. Chien, Y. H. Wang, B. R. Lin, and C. H. Liu,

-Implementation of an interleaved resonant converter for high-voltage applications, Proc. IET Power Electron., vol. 5, no. 4, pp. 447–455, Apr. 2012.

[8] C. H. Chien, Y. H. Wang, and B. R. Lin, —Analysis of a novel resonant converter with series connected transformers, IProc. IET Power Electron., vol. 6, no. 3, pp. 611–623, Mar. 2013.

[9] W. Li, Y. He, X. He, Y. Sun, F. Wang, and L. Ma, —Series asymmetrical half-bridge converters with voltage autobalance for high input-voltage applications, IIEEE Trans. Power Electron., vol. 28, no. 8, pp. 3665–3674, Aug. 2013.

[10] T. T. Sun, H. S. H. Chung, and A. Ioinovici, —A high-voltage DC-DC converter with Vin/3—Voltage stress on the primary switches, I IEEE Trans. Power Electron., vol. 22, no. 6, pp. 2124–2137, Nov. 2007.

[11] T. T. Sun, H. Wang, H. S. H. Chung, S. Tapuhi, and A. Ioinovici, —A highvoltage ZVZCS DC-DC converter with low voltage stress,IIEEE Trans. Power Electron., vol. 23, no. 6, pp. 2630–2647, Nov. 2008.

[12] H. Wang, H. S. H. Chung, and A. Ioinovici, —A class of high-input low output voltage single-step converters with low voltage stress on the primary-side switches and high output current capacity, IIEEE Trans. Power Electron., vol. 26, no.

6, pp. 1659–1672, Jun. 2011.

[13] J. R. Pinheiro and I. Barbi, —The three-level ZVS PWM converter—A new concept in high voltage DC-to-DC conversion, in Proc. IEEE Int. Conf. Ind. Electron. Control Instrum.Autom., 1992, pp. 173–178.

[14] R. Xinbo, L. Zhou, and Y. Yan, —Soft-switching PWM three-level converters, IIEEE Trans. Power Electron., vol. 16, no.5, pp. 612–622, Sep. 2001.

[15] W. Li, S. Zong, F. Liu, H. Yang, X. He, and B. Wu, —Secondary-side phase-shift-controlled ZVS DC/DC converter with wide voltage gain for high input voltage applications,IIEEE Trans. Power Electron., vol. 28, no. 11, pp. 5128–5139, Nov. 2013.